|

目前Y电容广泛的应用在开关电源中,但Y电容的存在使输入和输出线间产生漏电流,具有Y电容的金属壳手机充电器和一些特殊电器会让使用者有触电的危险,因此这些设备的制造商目前开始采用无Y电容的设计,然而摘除Y电容对EMI的设计带来了困难。具有频抖和频率调制的脉宽调制器可以改善EMI的性能,但不能绝对的保证充电器通过EMI的测试,必须在电路和变压器结构上进行改进才能使充电器满足EMI的标准。 1、EMI 常识

在开关电源中,功率器件高频开通、关断操作导致电流和电压的快速的变化是产生EMI的主要原因。

在电路中的电感及寄生电感中快速的电流变化产生磁场从而产生较高的电压尖峰: VL = LS · diL /dt

在电路中的电容及寄生电容中快速的电压变化产生电场从而产生较高的电流尖峰:

iC = C · duc /dt

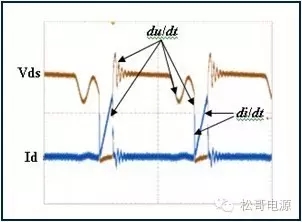

图1:MOSFET电压和电流波形

磁场和电场的噪声与变化的电压和电流及耦合通道如寄生的电感和电容直接相关。直观的理解,减小电压变化率du/dt和电流变化率di/dt及减小相应的杂散电感和电容值可以减小由于上述磁场和电场产生的噪声,从而减小EMI干扰。

1.1 减小电压变化率du/dt和电流变化率di/dt

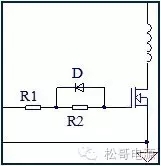

减小电压变化率du/dt和电流变化率di/dt可以通过以下的方法来实现:改变栅极的电阻值和增加缓冲吸引电路,如图2和图3所示。增加栅极的电阻值可以降低开通时功率器件的电压变化率。

图2:栅极驱动电路

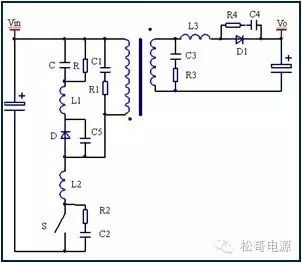

图3中,基本的RCD箝位电路用于抑止由于变压器的初级漏感在开关管关断过程中产生的电压尖峰。L1、L2和L3可以降低高频的电流的变化率。L1和L2只对特定的频带起作用。L3对于工作于CCM模式才有效。

R1/C1,R2/C2,R3/C3,R4/C4和C5可以降低相应的功率器件两端的高频电压的变化率。

所有的这些缓冲吸引电路都需要消耗一定功率,产生附加的功率损耗,降低系统的效率;同时也增加元件的数目和PCB的尺寸及系统的成本,因此要根据实际的需要选择使用。

图3:缓冲吸引电路

1.2 减小寄生的电感和电容值

开关器件是噪声源之一,其内部引线的杂散电感及寄生电容也是噪声耦合的通道,寄生电容包括漏源极电容和栅漏极的Miller电容,但是由于这些参数是器件固有的特性,电子设计和应用工程师无法对它们进行完全的抑制。减小开关管所在回路的尺寸并用宽的PCB 铜箔,可以最大限度地减小寄生电感。

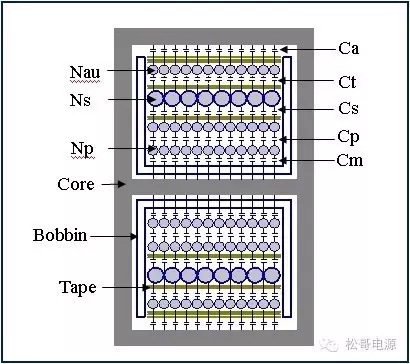

变压器是另外一个噪声源,而初级次级的漏感及初级的层间电容、次级的层间电容、初级和次级之间的耦合电容则是噪声的通道。初级或次级的层间电容可以通过减小绕组的层数来降低,增大变压器骨架窗口的宽度可在减小绕组的层数。分离的绕组如初级采用三明治绕法可以减小初级的漏感,但由于增大了初级和次级的接触面积,因而增大了初级和次级的耦合电容。采用铜皮的Faraday屏蔽可以减小初级与次级间的耦合电容。Faraday屏蔽层绕在初级与次级之间,并且要接到初级或次级的静点如初级地和次级地。Faraday屏蔽层使初级和次级的耦合系数降低,从而增加了漏感。

2、传导干扰

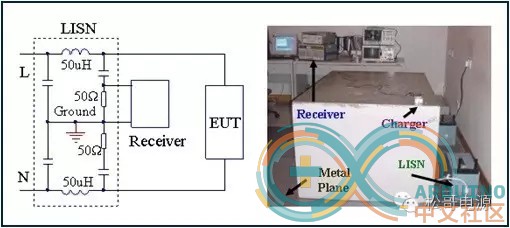

2.1 LISN

EMI测试由传导干扰CE和辐射干扰RE组成,这两种噪声分开的检测和评价。对于不同的应用,不同的地区和国家都有相应的标准,这些标准对于频段的宽度和限制值都作了十分明确的定义。例如对于手机充电器属于FCC15/EN55022

CLASS B,传导干扰测量的频率范围为0.15MHz到30MHz,辐射干扰测量的频率范围为30MHz到1GHz,具体的内容可以参考相关的标准FCC,CIRPR和EN等。

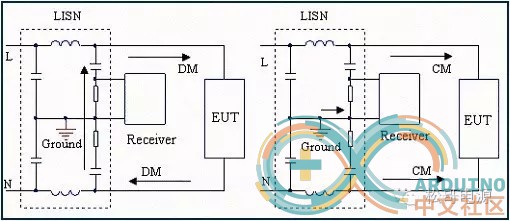

传导干扰指在输入和输出线上流过的干扰噪声,测试的方法见图4所示。待测试的设备EUT通过阻抗匹配网络LISN(或人工电源网络)连接到干净的交流电源上。

图4:LISN及EUT测试

LISN的作用如下:

① 隔离待测试的设备EUT和交流输入电源,滤除由输入电源线引入的噪声及干扰。 ② EUT产生的干扰噪声依次通过LISN内部的高通滤波器和50Ω电阻,在50 Ω电阻上得到相应的信号值送到接收机进行分析。

由图4可见:EUT放置在绝缘的测试台上,测试台下部装有接地良好的铁板,测试台及铁板的尺寸和安装都在特定的规定。

传导干扰来源于差模电流噪声和共模电流噪声,这两种类型的噪声干扰见图5所示,Y电容直接和传导干扰相关。

图5:差模电流和共模电流

差模电流在两根输入电源线间反方向流动,两者相互构成电流回路,即一根作为差模电流的源线,一根作为差模电流的回线。共模电流在两根输入电源线上同方向流动,它们分别与大地构成电流回路,即同时作为共模电流的源线或回线。

理论上1MHz以内主要是差模干扰,增大 X 电容就可以滤除差模干扰。5MHz以上主要是共摸干扰,可以通过以下方式滤除共摸干扰: ① 输入或输出加共模电感。 ② 加大对地Y电容,改变Y电容的连接方式。 ③ 调整输出的动点和静点位置。 ④ 变压器外面包铜皮,内部加铜皮屏蔽层。 ⑤ 变压器输出端和它连接的二极管或次极同步整流管之间串联小磁珠。 ⑥ 输出整流二极管或次极同步整流管加吸收电路。

1MHz-5MHz同时存在着差模、共模干扰,而且后面还会分析,差模和共摸干扰可以相互转化,因此在很多的系统中,非常难严格的区分差模、共模干扰,采用输入端并接更多电容并不能有效的完全滤除差摸干扰去分析干扰超标的差模和共模类型。

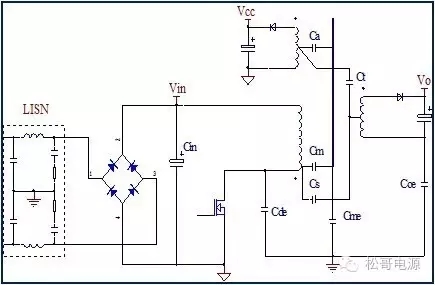

2.2 变压器模型

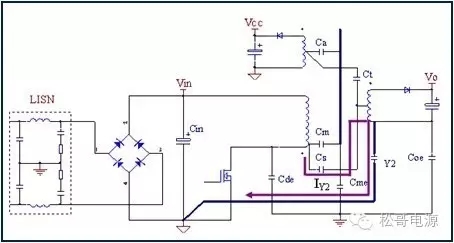

变压器包含寄生电容的模型见图6所示。 ① Cp: 初级绕组的层间电容。 ② Coe:输出线到大地的电容。 ③ Cme:磁芯到大地的电容。 ④ Ca:最外层绕组到磁芯的电容。 ⑤ Ct:辅助绕组到次级绕组的电容。 ⑥ Cs:初级绕组到次级绕组的电容. ⑦ Cm:最内层初级绕组到磁芯的电容。

图6:变压器寄生电容

2.3 差模电流

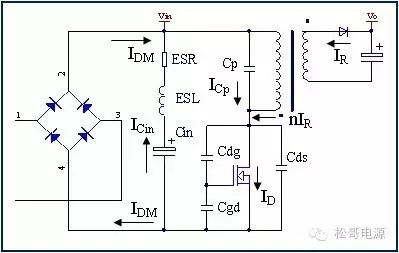

差模电流噪声主要由功率开关器件的高频开关电流产生。

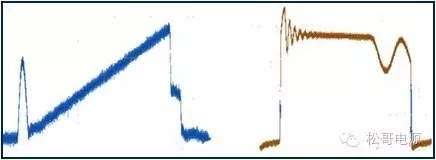

(1)功率器件开通 功率器件在开通的瞬间,存在着电流的尖峰,如图7所示。

图7:开通电流尖峰

开通电流尖峰由三部分组成:

① 变压器初级绕组的层间电容充电电流。 ② MOSFET漏源极电容的放电电流。 ③ 工作在CCM模式的输出二极管的反向恢复电流。

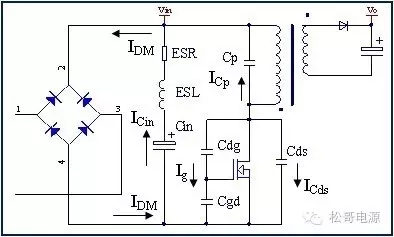

开通电流尖峰不能通过输入滤波的直流电解电容旁路,因为输入滤波的直流电解电容有等效的串联电感ESL和电阻ESR,这样就产生的差模电流在电源的两根输入线间流动。MOSFET漏源极的电容的放电电流对差模电流噪声无影响,但会产生辐射干扰。

图8:功率器件开通瞬间的差模电流

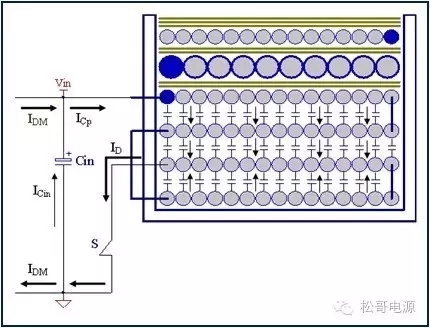

功率器件开通瞬间形成的差模电流为IDM为: IDM = ICp + n·IR - ICin

对于变压器而言,初级绕组两端所加的电压高,初级绕组的层数少,层间的电容越少,然而在很多应用中由于骨架窗口宽度的限制并为了保证合适的饱和电流,初级绕组通常用多层结构。本设计针对四层的初级绕组结构进行讨论。

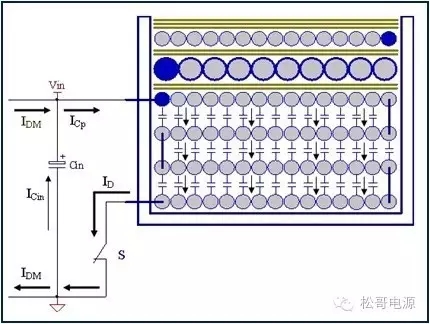

图9:开关管开通时初级绕组层间电流方向

对于常规的四层初级绕组结构,在开关管开通和关断的过程中层间的电流向同一个方向流动。在图9中,在开关管开通时,源极接到初级的地,B点电压为0,A点电压为Vin,基于电压的变化方向,初级绕组层间电容中电流流动方向向下,累积形成的差模电流值大。

(2)功率器件关断

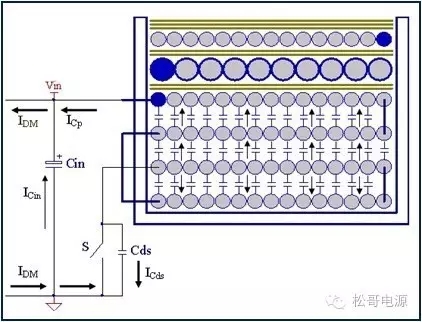

在功率器件关断瞬间,MOSFET漏源极电容的充电,变压器初级绕组的层间电容放电,这两部分电流也会形成差模电流,如图10所示。

图10:功率器件关断瞬间的差模电流

功率器件关断瞬间形成的差模电流为IDM为: IDM = ICds + Ig - ICp - ICin

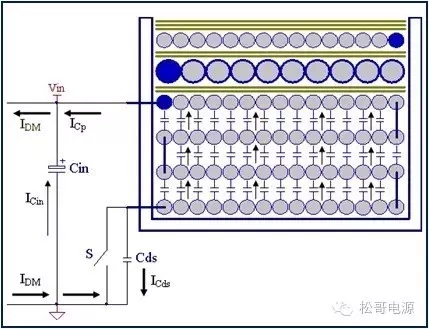

图11:开关管关断时初级绕组层间电流方向

同样基于电压的变化方向,初级绕组层间电容中的电流流动方向向上,累积形成的差模电流值大。

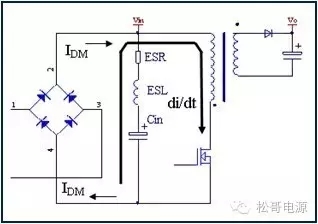

(3)功率开关工作于开关状态

功率开关工作于开关状态,开关电流(开关频率)的高次谐波也会因为输入滤波的直流电解电容的ESL和ESR形成差模电流。

图12:开关电流形成的差模电流

差模电流可以通过差模滤波器滤除,差模滤波器为由电感和电容组成的二阶低通滤波器。从PCB设计而言,尽量减小高的di/dt的环路并采用宽的布线有利于减小差模干扰。

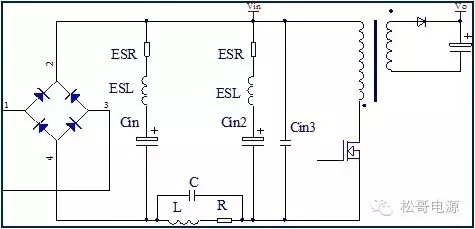

由于滤波器的电感有杂散的电容,对于高频的干扰噪声可以由杂散电容旁路,使滤波器不能起到有效的作用。用几个电解电容并联可以减小ESL和ESR,在小功率的充电器中由于成本的压力不会用X电容,因此在交流整流后要加一级LC滤波器,如图13所示。

图13:差模滤波器

如果对变压器的结构进行改进,如图14和15所示,通过补偿的方式可以减小差模电流。初级绕组的热点应该埋在变压器的最内层,外层的绕组起到屏蔽的作用。

同样的基于电压的变化方向,可以得到初级绕组层间电容的电流流动的方向,由图14和15所示可以看到,部分的层间电流由于方向相反可以相互的抵消,从而得到补偿。

图14:新结构开关管开通时初级绕组层间电流流动方向

图15:新结构开关管关断时初级绕组层间电流流动方向

2.4 共模电流

共模电流在输入及输出线与大地间流动,其产生主要是功率器件高频工作时产生的电压的瞬态的变化。共模电流的产生主要有下面几部分:

① 通过MOSFET源级到大地的电容Cde。 ② 通过Cm和Cme产生共模电流。 ③ 通过Ca和Cme产生共模电流。 ④ 通过Ct和Coe产生共模电流。 ⑤ 通过Cs和Coe产生共模电流。

对于电容Cde,如果改进IC的设计如对于单芯片电源芯片,将MOSFET源极连接到芯片基体用于散热而不是用漏极进行散热,这样可以减小漏极对大地的寄生电容。PCB布线时减小漏极区铜皮的面积可减小漏极对大地的寄生电容,但要注意保证芯片的温度满足设计的要求。

通过Cs和Coe产生共模电流部分在总的共模电流中占主导作用。减小漏极电压的变化幅值及变化率可减小共模电流,如降低反射电压,加大漏源极电容,但这样会使MOSFET承受大的电流应力,其温度将增加,同时加大漏源极电容产生更大的磁场发射。

图16:共模电流产生

图17:Y电容作用

电压如果系统加了Y电容,由图17所示, 通过Cs的大部分的共模电流被Y 电容旁路返回到初级的地,因为Y电容的值大于Coe。Y电容必须直接并用尽量短的直线连接到初级和次级的冷点。作为一个规则,如果开通叶MOSFET的dV/dt大于关断时的值,Y电容连接到初级的地。反之连接到Vin。

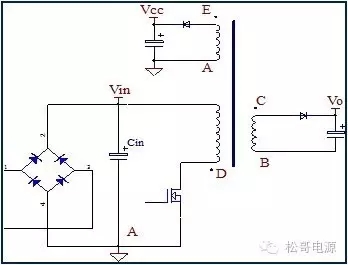

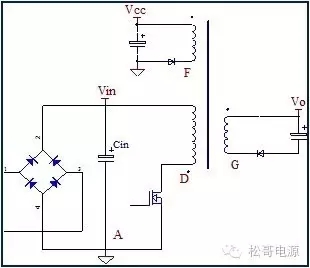

电压没有变化的点称为静点或冷点,电压变化的点称为动点或热点。初级的地和Vin都是冷点,对于辅助绕组和输出绕组,冷点可以通过二极管的位置进行调整。图18中,A、B和Vin为冷点,E、D、和C为热点;而图19中,A、Vcc、Vin和Vo为冷点,D、F和G为热点。

图18:冷点位置

图19:改变二极管后冷点位置

去除Y电容无法有效的旁路共模电流,导到共模电流噪声过大,无法通过测试标准,设计的方法是改进变压器的结构。一般的法加利屏蔽方法不能使设备在无Y电容的情况下通过EMI的测试。由于MOSFET的漏极端的电压变化幅值大,主要针对这个部位进行设计。

电流及电压的变化是产生差模及共模电流的主要原因,也是影响EMI的最主要的原因,特别是电压变化,寄生电容是其流动的通道。

前面提到Cm和Cme及Cme和Ca也会产生共模电流,初级层间电容的电流一部分形成差模电流,有一部分也会形成共模电流,这也表明差模和共模电流可以相互的转换。

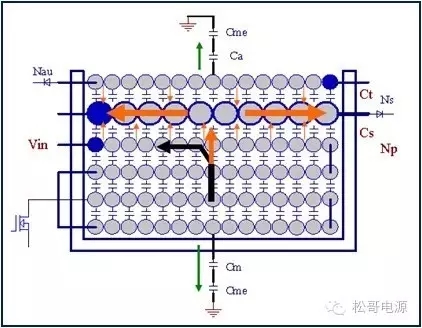

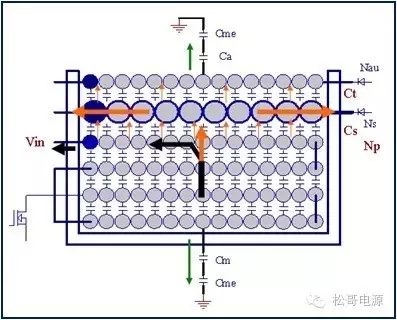

如果按图20结构安排冷点(蓝色点)和绕组,在没有Y电容时基于电压改变的方向可以得到初级绕组与次级绕组以及辅助绕组和次级绕组层间电容的电流的流动方向,初级绕组和辅助绕组的电流都流入次级绕组中。

图20:初级与次级绕组及辅助和次级绕组共模电流

图21:调整冷点后初级与次级绕组及辅助和次级绕组共模电流

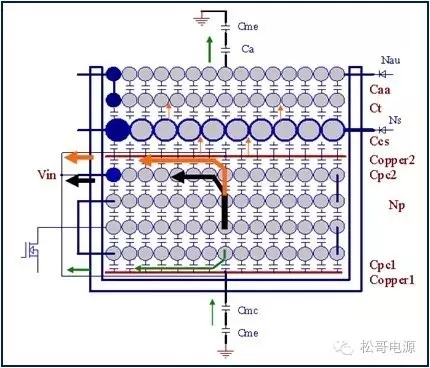

调整冷点后如图21所示,可以看到初级绕组与次级绕组及辅助绕组和次级绕组层间电容的电流的流动方向相同,可以相互抵消一部分流入次级绕组的共模电流,从而减小总体的共模电流的大小。

辅助绕组和次级绕组的整流二极管放置在下端,从而改变电压变化的方向,同时注意冷点要尽量的靠近,这样因为两者间没有电压的变化,所以不会产生共模电流。

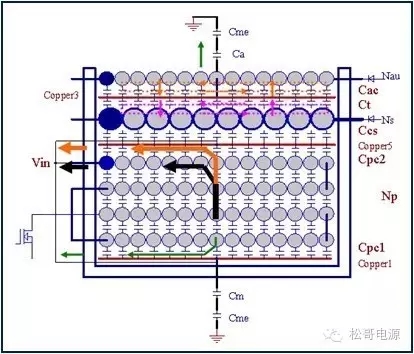

进一步如果在内层及初级绕组和次级绕组间放置铜皮,铜皮的宽度小于或等于初级绕组的宽度,铜皮的中点由导线引线到冷点,如图22所示,由于铜皮为冷点,与其接触的绕组和铜皮间电压的摆率降低,从而减小共模电流,同时将共模电流由铜皮旁路引入到冷点。注意铜皮的搭接处不能短路,用绝缘胶带隔开,内外层铜皮的方向要一致。

图22:铜皮的补偿

辅助绕组和次级绕组的共模电流可以由以下方法补偿:

① 加辅助屏蔽绕组

辅助屏蔽绕组绕制方向与次级绕组绕制方向保持一致,辅助屏蔽绕组与次级绕组的同名端连接到一起并连接到冷点,辅助屏蔽绕组的另一端浮空。由于它们的电压变化的方向相同,所以两者间没有电流流动。

② 加外层的辅助屏蔽铜皮

辅助屏蔽铜皮的中点连接到到辅助绕组的中点。同样,基于电压的变化方向分析电流的流动方向,可以看到,两者之间的电流形成环流,相互补偿抵消,从而降低共模电流。

图23:辅助屏蔽铜皮

3、EMI 辐射干扰

3.1 电场和磁场发射

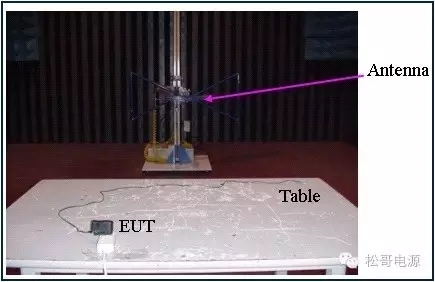

辐射干扰的测试在专门的屏蔽室中进行,待测试的设备放在转台上,天线分别放在水平和垂直的位置上下移动扫描,检测到信号送到接收机进行分析。

图24:辐射干扰测试

辐射干扰的测试包括电场发射和磁场发射,电场发射由du/dt产生,磁场发射由di/dt产生。空间电容是电场发射的通道,共模电流可以产生相当大的电场发射。

图25:电场发射

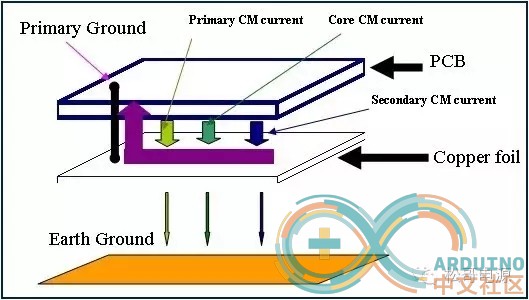

初级绕组电压变化的幅值大,对于电场发射起主导作用。磁芯也是一个电场发射源。在系统的PCB底层铺铜皮或额处加一块铜皮或单面板,可以有效的减小电场发射和共模电流,这也是多层PCB板的设计中经常将第二层作为完整的地层的原因。

图26: 减小电场发射

高di/dt 的环路通过环路的寄生电感产生磁场发射,次级侧的电流变化幅值大,对于磁场发射的起主导作用。磁场发射形成的方向见图27所示,方向符合右手定则。

高di/dt环路的寄生电感随环路面积增大而增大,因此磁场发射对于PCB的设计非常关键。次级侧的电流环面积要尽量的小,布线要尽量的短粗。

图27: 磁场发射

变压器的杂散磁场也是一个磁场发射源,其主要由变压器的气隙产生。E型磁芯在两侧开气隙时杂散磁场大,在中心柱开气隙时杂散的磁场小。在变压器的最外面包裹铜皮,铜皮两端短接,用导线连接到冷点,可以减小杂散的磁场。因为杂散磁场在铜皮中产生涡流,涡流反过来产生磁场阻碍变压器杂散磁通的外泄。输出棒状及鼓状的差模电感如同一个天线产生大的磁场发射。使用前述的相关的缓冲吸引电路可以减小相应的磁场发射。 图28:输出线发射

手机充电器要带长的输出线1.8m进行测试,长的输出导线也如同一个天线,并将共模电流放大,从而形成较大的共模电场辐射,这种辐射只有通过上面变压器的结构进行抑止,在没有频率拌动或频率调制的系统中还得加输出共模电感,才能有效的减小在40~60M间的电场发射。

通常40-60MHz干扰由功率 MOSFET的快速开通和关断产生,特别是次级同步整流管的关断,对这个频率段EMI影响非常大。有些资料认为可以用增大 MOSFET的栅极驱动电阻可以进行抑止,事实上很多时候这个方法并不有效,比较有效的方法是并接RC缓冲吸收电路,并且吸收电容C要足够大,将dV/dt降到一定的值如2V/ns以下,才可以保证系统EMI有足够的裕量,吸收电阻R的值将影响系统的效率和电压尖峰。

80-150MHz干扰与输出整流二极管的反向恢复特性或次级同步整流管的关断特性相关,在输出整流二极管或次级同步整流管的漏极串联具有特征阻抗的小磁珠,可以有效的抑止这个频段的干扰。当然有些客户不太喜欢采用这种方案,那么就要采用其它的方法或对器件本身进行优化。

3.2 共模电感设计

共模电感的两个绕组分别与输出的二根线串联,当输出电流在每个绕组流过时它们在磁芯中形成的磁通方向是相反的,可以相互的抵消,平衡的条件下磁芯中的磁通为0,因此共模电感不会因为输出的负载电流产生饱和。当同方向的共模电流在两个绕组中流过时,其在磁芯中形成的磁通方向是相同,阻抗增加,从而衰减共模电流信号。

图29: 共模电感

设计过程:

① 选择磁芯材料 铁氧体是一个较好的具有成本优势的材料。

② 设定电感的阻抗 对于一个给定的要求衰减的频率,定义此频率下共模电感的感抗为50~100Ω,即至少50%的衰减,因此有: Z = w·L

对于输入交流的共模电感,设计时还要考虑到电感对于输入50Hz信号必须是几乎没有衰减的全部通过。

③ 选择磁芯的形状的和尺寸 成本低漏感小的环形磁芯非常适合于共模电感,但是这种形状不容易实现机械化绕制,一般用手工绕制。磁环尺寸的大小选取有一定的随意性,通常基于PCB的尺寸选取合适的磁芯。为了减小共模电感的寄生电容,共模电感通常只用单层的线圈。若单层绕制时磁芯无法容纳所有的线圈,则选用大一号尺寸的磁环。当然也可以基于磁芯的数据手册由LI的乘积选取。

④ 计算线圈的匝数 由磁芯的电感系数AL计算共模电感的圈数: N = (L /AL)0.5

⑤ 计算导线的线径 导线允许通过的电流密度选取为:400~800A/cm²,由此可以得到要求的线径。

3.3 频抖Jitter和频率调制

事实上噪声是基于特定的频带和步长(传导是9KHz)来检测的,当开关频率固定时,基于开关频率的电流变化和电压变化的高频高次谐波如2次,3次,4次,…… 会在一个特定的频率点处叠加,这样以此频率点为中心的一个窄带内噪声的值就较高。

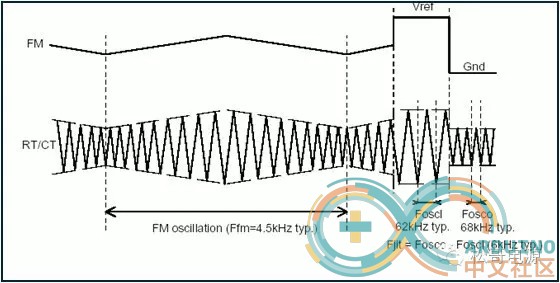

芯片有频抖和频率调制时,开关的频率不是固定的而是在一定的范围内变化,频率变化的范围通常以名义的开关频率为中心上下变化不大于4KHz,以免影响到系统的正常工作。如基频即工作频率变化范围为±4KHz,则2次谐波频率变化的范围为±8KHz,3次谐波频率变化的范围为±12KHz ……,这样对于一个特定的频率点噪声在更宽的频带内分布,因此噪声的值降低。频率越高,特定的频率点频带分布越大,噪声值也就越低。频抖和频率调制的原理见图28所示。

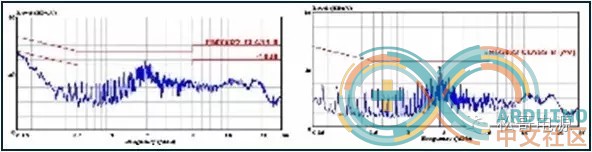

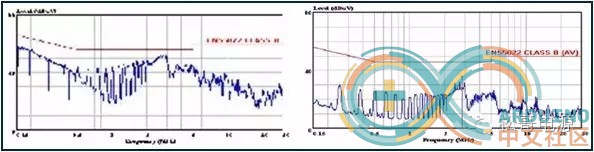

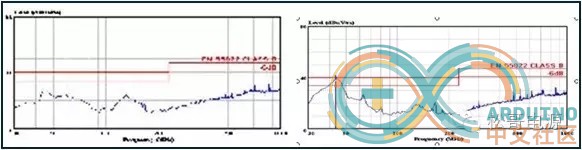

从图31至图34可以看到:没有频抖和频率调制时谐波分布窄,噪声值在谐波频率点处较高。有频抖和频率调制时,谐波值平滑而且较小,从图31至图34还可以看出:频抖和频率调制对准峰值降低不大,而对平均值降低十分时显。在测试RE时,由于频抖和频率调制的作用,即使从波形看某一频点似乎没有余量,但接收机在读点时很难抓取到幅值最大点,因此读点时读取值仍有范围内有一定余量。

图30:频抖和频率调制原理

图31:传导测试无频抖和频率调制准峰值和平均值

图32:传导测试有频抖和频率调制准峰值和平均值 图33:辐射测试无频抖和频率调制水平和垂直值

图34:辐射测试有频抖和频率调制水平和垂直值

EMI的传导和辐射的标准是使用准峰值和平均值,在实际测量过程中由于准峰值的测量速度慢非常耗时间,所以通常使用峰值和平均值来测量。如果峰值低于准峰值标准6dB或7dB以上,那么认为测试通过;如果峰值和准峰值标准的差值不到6dB或7dB,那么就通过读点的方法测量实际的准峰值,检查是否可以通过测量标准。

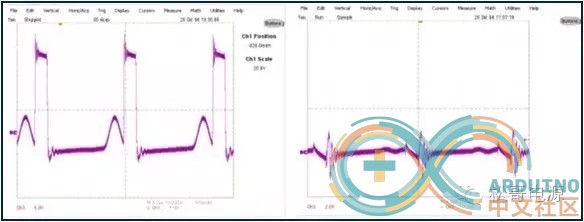

3.4 浮空电压波形 测量变压器初级和次级静点的电压波形及变压器磁芯的电压波形可以为EMI的传导测试提供一些参考。常规结构的变压器的初级和次级静点电压波形的幅值为10V并且可以明显的看到基于开关频率的开关波形。新的结构的变压器的初级和次级静点电压波形的幅值为5V,基于开关频率的开关波形不是很明显。

常规结构的变压器的磁芯电压波形的幅值为18V并且可以明显的看到基于开关频率的开关波形。新的结构的变压器的磁芯电压波形的幅值为5V,基于开关频率的开关波形不是很明显。

(a)常规结构 (b)新的结构 图35:初级和次级静点电压波形 (电压:5V/格, 时间:4us/格)

(a)常规结构 (b)新的结构 图36:磁芯电压波形 (电压:5V/格, 时间:4us/格)

附录

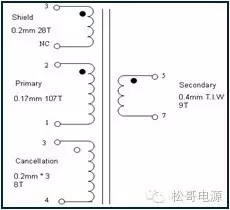

1、本设计采用变压器结构,芯片没有频抖和频率调制功能,芯片需要辅助绕组供电 ① 内层铜皮屏蔽层,铜皮宽度小于初级绕组宽度,中点引线接到Vin。 ② 二层初级绕组。绕制要尽量的平齐,不要漏圈和错圈。另外二层初级绕组。绕制要尽量的平齐,不要漏圈和错圈。如此绕制漏极所接的初级端埋在内部。 ③ 第二层铜皮屏蔽层,铜皮宽度小于初级绕组宽度,中点引线接到Vin。 ④ 次级绕组。 ⑤ 辅助屏蔽绕组,起点接Vcc,另一端浮空,与辅助绕组同方向同圈数绕制。 ⑥ 辅助绕组。

挡墙仅绕在初级侧,次级侧不用挡墙。初级、屏蔽和辅助绕组紧靠靠骨架窗口初级侧对齐绕制,次级绕组紧靠窗口次级侧对齐绕制,两者错开减小寄生电容。次级绕组与辅助屏蔽绕组及屏蔽铜皮层至少加二层绝缘胶带。

2、PI 无Y电容的变压器结构 ① 芯片有频抖功能,芯片可以不需要辅助绕组供电。 ② 变压器最外面裹铜皮,铜皮两端短接并引线到初级的地。

图附1:脚管和绕组安排

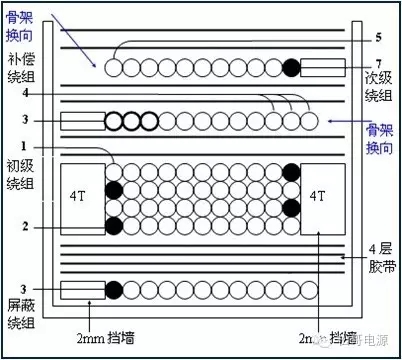

其中:实心黑点圈为绕制时的起点,空心点为骨架换方向后绕制时的起点。具体的各绕组的在骨架内的分布如下图所示。

图附2:PI变压器的结构

3、余量更大变压器结构,芯片没有频抖和频率调制功能,芯片需要辅助绕组供电 ① 内层屏蔽绕组,与初级同线径同单层圈数,且和最内层初级同方向绕制,绕制起点接初级的地,另一端浮空。 ② 四层初级绕组。绕制要尽量的平齐,不要漏圈和错圈。 ③ 第二层屏蔽绕组,与初级同方向绕制,起点接初级的母线电压点。 ④ 铜皮屏蔽层,铜皮宽度小于初级绕组宽度,中点引线接到初级地。 ⑤ 辅助绕组。 ⑥ 次级绕组。

挡墙仅绕在初级侧,次级侧不用挡墙。初级、屏蔽和辅助绕组紧靠靠骨架窗口初级侧对齐绕制,次级绕组紧靠窗口次级侧对齐绕制,两者错开减小寄生电容,次级绕组与辅助绕组间至少加三层绝缘胶带。

参考文献 Bob Mammano and Bruce Carsten, TI seminar: Understanding and Optimizing Electromagnetic Compatibility in SMPS ——文章来源:融创芯城

|