|

射频PCB板设计是开发中关键一环,这里我们以WLAN芯片的PCB为例来具体谈一下PCB layout的设计要点。

WLAN和蓝牙芯片的开发板的设计重点,可以分为电源部分,晶振部分,射频部分及接口(I/F)部分。下面我们分布谈一下各部分的设计思想和注意点。

一、首先是电源部分,

着手设计PCB之前,首先需要仔细查看SOC的电源拓扑结构,比如常见的40nm/28nm的WLAN芯片,它的电源常分为1.2V Buck Regulator,2.5V Regulator,3.3V Regulator。低电压Reg主要供数字及PLL部分使用,高电压Reg主要供射频PA使用。各Buck输出部分,一般都有输出物理端口, 这是因为输出端口接各个block是采用星型拓扑结构,在下一级有物理输入接口,应用中需要接旁路电容。电源部分的layout设计主要有两大问题,Cbuck的输出电感,旁路电容的选取及设置,还有电源走线的设计。

旁路电容的选取对各Buck输入/输出 noise,输出电压性能有重要影响。现在的Buck DC regulator采用PFM (Pulse Frequency Modulation)方式的较多。相比以前的方式,PFM一般有更小的Vout Ripple电压。输出一般都串接大电感后在接去耦电容。

电感的选取,建议参考各家SOC Vendor推荐的型号。如果考虑成本选取其他Local厂商时,务必要check DCR(影响定格电流,效率),ACR(影响AC Loss)还有最大定格电流和电感&DC电流的profile图。这几个参数对电感来说都是相互关联的,一般DCR高的话,定格电流就低。有条件的话,可以之间测一下Ind端AC信号,看看Peak-peak电压变化情况。

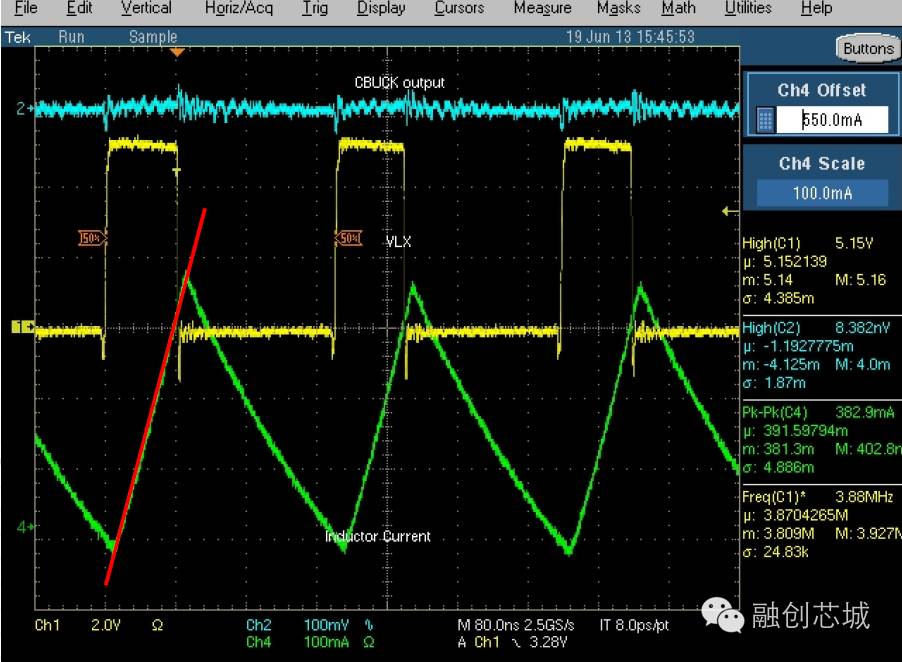

下面是一例实测CBuck的输出电压,电流波形,输出波形(蓝色)相对稳定,电感上的电流波形保持稳定的线性特性,600mA的DC偏置输出,AC电流变化差不多380mA 。 设计问题不大。

去耦电容的选取要考虑到电流capacity,定格最大电压及误差。要确保实际有效去耦电容的设置,要尽量靠近Reg输入输出端,在星型拓扑结构里,电容要安置在星型节点附近。 这是因为每个拓展出去的电源trace都会产生电感效应。主节点放置大容量的电容可以起到高频噪声滤波功能。

电源的布线,要重点考虑2点: 1)避开对其他对noise敏感的布线的coupling; 2)降低电源EMI loop的影响。

先谈谈第1点,对noise敏感的布线,比如SOC的一些总线,RF相关端口,还需要查看datasheet的keep out区域。对一些功耗大的Reg电源布线要充分考虑到散热设计。一般来说SOC的主Buck的输入输出pin也常分布在芯片的转角附近,这样的Pin布局,有利于PCB设计,电源的布线考虑到散热效应,一般在layer1,layer2上的较多。电源的接地设计,依据PCB层数, 有条件的话, 可以单独设置一层放PMU布线。在WLAN设计里,一般性都采用4层以上的PCB,第一层(top)一般设计成PMU的GND island,与周边的其他布线加强隔离度。

第2点是 EMI loop, 现代SOC的switching 电源本身就是个noise源,如何优化EMI Loop是个必须关心的问题。Cbuck的输入侧的Loop和输出侧的loop,每个loop经电源输入或输出端口,经过旁路电容,再到ground。每个Loop都要设计成尽可能短的物理layout,确保noise不会干扰的其他布线。电源走线在上下层改变时,要尽可能设计多的过孔()2个)。

二、谈谈晶振(Xtal)部分。

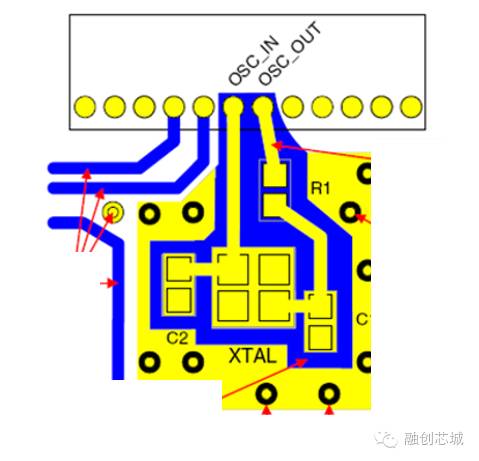

随着SOC设计及工艺提高,以前常见的PLL LPF外接,最近一般都完全设计在芯片里面了。 所以晶振部分成了PLL这一环主要care的问题。一般现在的mobile应用, 常用到19.2MHz, 26MHz,及37.4MHz的频率。Xtal 电容值的选取超过了本文的scope,这里略过主要谈谈xtal的布线。常见的xtal都是带输入,输出的端子。 曾经有遇到过最深刻的一个问题就是Xtal对RF端口之间产生影响,晶振频率的谐波能量导致了认证测试失败。后来吸取教训,在xtal的top layer布线(输入,输出及xtal cap的布线)设计成独立的island。(参考下图)如果space不允许的话,至少简易在xtal靠近RF一层,在GND里加一条Slot, 也可以降低xtal谐波干扰的风险。

Xtal布线的下面一层,建议不要设计其他敏感的走线(比如I/F,其他电源走线等)。

三、谈一下射频部分的走线要点。

总的来说,现在主流的WLAN SOC芯片,Rx的性能相比Tx性能,spec上余量更多,所以布线的时候,一般常优先考虑Tx侧的布线。比如FEM可以设计在离Tx近一点的地方。RF走线(50欧)设计,常用的方法是:

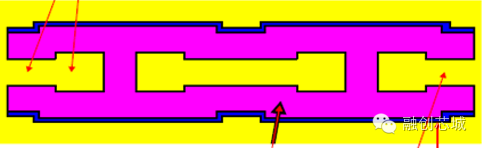

1 )挖空下面一层的metal,使50ohm线宽变粗,减少走线和元件pad的不连续性。

2 )RF走线两端的GND一定要设计尽可能多的GND via。特别是在最后接ANT的地方, GND via过少直接会影响到RF loss。

3 )RF走线一般尽量少弯曲90度以上,space余度不多的地方,可以90度弯曲。

4 )注意Tx和Rx之间的isolation,现在的WLAN芯片,很多都是2x2以上的MIMO,射频部分的走线变得愈加复杂。虽然WLAN采用的是TDM方式,但是在FEM的layout pattern设计,还是兼顾电源,Tx和Rx的coupling影响。

四、接口部分的走线设计。

作者接触到SDIO,SPI及PCIE的I/F较多。接口bus速度越快,对layout设计要求越高。 SDIO 3.0的话,保证每个走线都是50ohm并且长度要小于10cm,确保各数据线间的走线长度差要小于100mil (2.54mm 相当于17.5ps jitter)。 走线一般满足thumb of rule即2:1的经验公式,比如trace width=4mil, 则gap最好8mil以上。另外clock走线最容易产生noise,所以clock走线要与其他数据线隔开,最好加入gnd glitch。

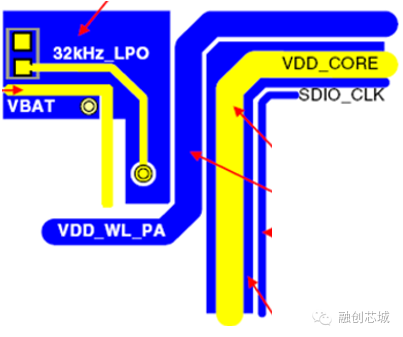

接口的走线一般都是比较noise敏感的,尽量避开和电源走线layer的交迭重合。 比如下面一例,电源层(蓝色)和数据接口层(黄线)在层与层上面尽量做到没有交迭重合。主要电源走线的下面layer一般布置了GND走线。

在实际应用中, 常常会首先遇到是单面PCB设计还是双面PCB设计。如果是单面PCB设计的话,各路元件的布置需要远近取舍,考虑优先度。

还有部分朋友接触的可能不是SOC芯片,而是集成了SOC芯片的模块,比如Murata, TDK等厂商的WLAN模块。这些模板因为内部完成了对Xtal,RF FEM/Trace的集成,进一步降低了PCB的设计,但是对电源走线,还是需要PCB板级设计的注意。

小结

此文主要介绍了射频SOC芯片的PCB板设计的4大要点,其实每个要点都离不开GND的配置设计。 在客户的设计案例中,我们也遇到不少因为layout设计缺陷而改版的案子,很多问题我们在上面都已谈到,相信不少同领域的朋友应该会有同感。

--------------------------------------融创芯城-----------------------------------

|